## USN

## Third Semester B.E. Degree Examination, Dec. 07 / Jan. 08 Analog Electronic Circuits

Time: 3 hrs. Max. Marks:100

Note: Answer any FIVE full questions.

1 a. What do you understand by 'reverse recovery time' of a diode? Explain. (05 Marks)

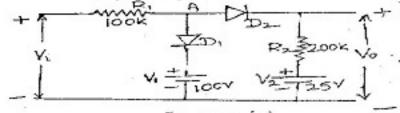

The input voltage V<sub>i</sub> to the two level clipper circuit [as shown in Fig. Q1(b)] varies linearly from o to 150 V. Sketch the output voltage V<sub>0</sub> to the time scale. Assume diodes as ideal.<sup>6</sup>

Fig. Q1(b) (10 Marks)

Draw and explain the working of the clamper circuit which clamps the positive peak of a signal to zero volts. (05 Marks)

2 a. Explain the circuit of a transistor switch being used as an inverter. (05 Marks)

Derive an expression for the stability factor, S(Ico), of the voltage divider Bias circuit. (06 Marks)

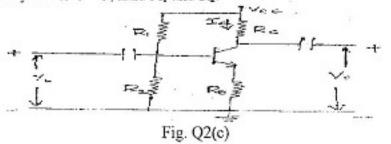

c. In the circuit of Fig. Q2(c)  $V_{CC} = 10 \text{ V}$ ,  $R_C = 1.5 \text{ k}\Omega$ ,  $I_C = 2 \text{ mA}$ ,  $V_{CE} = 5 \text{ V}$ ,  $V_{BE} = 0.7 \text{ V}$ , 3 = 50 and stability factor S = 5, find  $R_1$  and  $R_2$ .

(09 Marks)

3 I lette the expressions for A<sub>V</sub>, A<sub>I</sub>, Z<sub>I</sub> and Z<sub>0</sub> for CE fixed bias configuration using complete hybrid equivalent model. (12 Marks)

For common base amplifier shown in Fig Q3(b), determine Z<sub>i</sub>, A<sub>I</sub>, A<sub>V</sub> and Z<sub>0</sub> using a traplete hybrid equivalent model.

Given

$$h_{ie} = 1.6k\Omega$$

,  $h_{fe} = 110$  (08 Marks)

$h_{re} = 2 \times 10^{-4}, h_{oe} = 20 \mu S.$

Fig. Q3(b)

The input power to a device is 10,000 W at a voltage of 1000 V. The out put power is 500W and the output impedance is 20Ω.

Find power gain in decibels, ii) Find voltage gain in decibels. (04.)

Describe miller effect and derive an equation for miller input and output capacitances.

Discuss the factors that affect the low frequency response of a BJT-CE amplifier. (10 Marks)

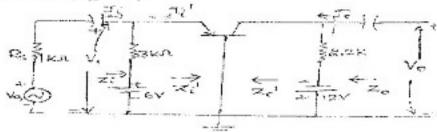

Fig. Q5(a) shows cascading of an emitter follower circuit and a common base circuit. 5 i) The loaded gain of each stage The total gain for the system, A<sub>V</sub> and A<sub>VS</sub>. iii) The total current gain for the system iv) The total gain far the system if the emitter follower circuit were removed. Avz COMMON follower Zi =IOKA Zi=26JL Zo=12.02 Zo=5.1K HUNC =1 AVNL=240 Ki=Zi 20520 Fig. Q5(a) Show that negative feedback increases the bandwidth of an amplifier. Derive an expression for output resistance of a voltage series feedback amplifier. (05 Ma a. With the help of a circuit diagram, explain the working of class-B pushpull ampli 6 Obtain an expression for maximum conversion efficiency of this amplifier. b. Discuss the different types of power amplifiers. (09 Ma c. For distortion readings of  $D_2$  = 0.15,  $D_3$  = 0.01 and  $D_4$  = 0.05 with  $I_1$  = 3.3 Amps (05 Ma  $R_C = 4\Omega$ . Find - i) Total harmonic distortion D, ii) Fundamental power component (06 Ma 7 What is Barkhausen criterion? Explain how oscillations start in an oscillator. b. With the help of a neat circuit diagram, explain transistor colpitts oscillator. Write (97 Mar expression for the frequency of oscillation. (08 Mar c. A quartz crystal has L = 0.12 H, C = 0.04 pF  $C_M = pF$  and R = 9.2 k $\Omega$ . Find i) Series resonant frequency, ii) Parallel resonant frequency. (05 Mar 8 Discuss the differences between FET and BJT. Derive the expressions for Z<sub>i</sub>, Z<sub>o</sub> and A<sub>V</sub> for common drain JFET amplifier. (04 Mark c. A dc analysis of source follower network shown in Fig. Q8(c) results in V<sub>GSQ</sub> = -2.86 (09 Mark and  $I_{DO} = 4.56$  mA. Determine i)  $g_m$ , ii)  $r_d$ , ii)  $Z_i$ , iv)  $Z_0$  with and without  $r_d$ . v)  $A_V$  with and without  $r_d$ .  $I_{DSS} = 16 \text{mA}, V_P = 4V, Y_{OS} = 25 \mu\text{S}.$ 0.05.47 Fig. Q8(c) (07 Marks) \*\*\* 2 of 2